- 产品详情

功能描述:

CY7C372i是一款系统内可重编程复杂可编程逻辑器件(CPLD),是FLASH370i™高密度高速CPLD系列的一部分。与FLASH370i系列的所有成员一样,CY7C372i旨在为高密度cpld带来22V10的易用性和高性能,以及PCI本地总线规范支持。

与所有UltraLogic™FLASH370i器件一样,CY7C372i具有电擦除和ISR功能,简化了设计和制造流程,从而降低了成本。Cypress ISR功能是通过JTAG串行接口实现的。数据通过SDI和SDO引脚输入和输出。ISR接口通过编程电压引脚(ISREN)使能。此外,由于FLASH370i器件具有优越的可路由性,ISR通常允许用户在固定引脚分配的同时更改现有的逻辑设计。

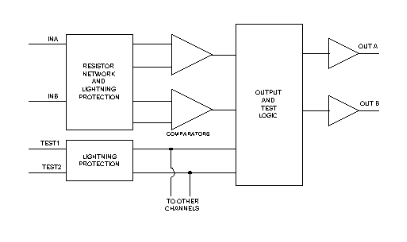

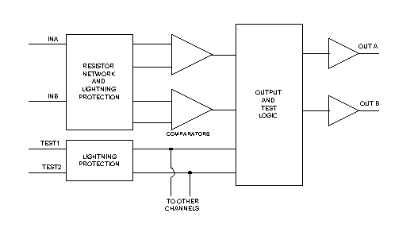

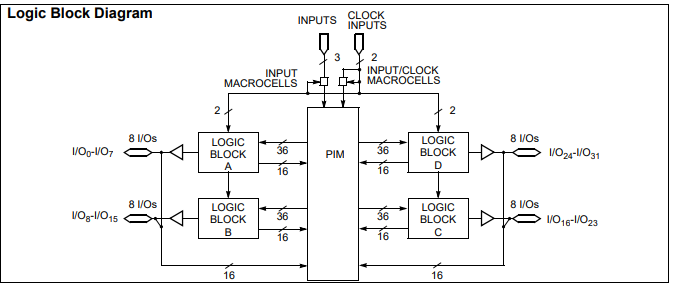

CY7C372i中的64个巨细胞被分成4个逻辑块。每个逻辑块包括16个宏单元、一个72 × 86的产品项数组和一个智能产品项分配器。

FLASH370i架构中的逻辑块已连接具有非常快速和可预测的路由资源可编程互连矩阵(PIM)。PIM为互连带来了灵活性、可路由性、速度和统一的延迟。

特性:

•64个宏单元在四个逻辑块

•32个I/O引脚

•五个专用输入,包括两个时钟引脚

•系统内可编程(ISR™)闪存技术- JTAG接口

•所有I/ o和专用输入的总线保持能力

•没有隐藏的延迟

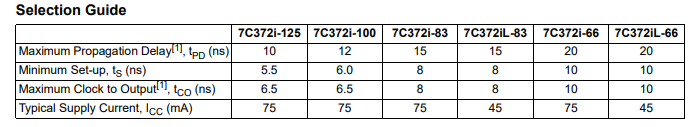

•高速

—fMAX = 125 MHz

- tPD = 10ns

- tS = 5.5 ns

- tCO = 6.5 ns

完全符合PCI标准

•3.3V或5.0V I/O操作

•可在44引脚PLCC, TQFP和CLCC封装

•与CY7C371i引脚兼容

产品技术规格:

| EU RoHS | Not Compliant |

| ECCN (US) | 3A001.a.2.c |

| Part Status | Obsolete |

| HTS | 8542.39.00.01 |

| Automotive | No |

| PPAP | No |

| Family Name | FLASH370i |

| Program Memory Type | Flash |

| Number of Logic Blocks/Elements | 4 |

| Number of Global Clocks | 2 |

| Number of Macro Cells | 64 |

| Product Terms | 16 |

| Device System Gates | 1600 |

| Data Gate | No |

| Maximum Number of User I/Os | 32 |

| In-System Programmability | Yes |

| Programmability | Yes |

| Reprogrammability Support | Yes |

| Maximum Clock to Output Delay (ns) | 10 |

| Maximum Propagation Delay Time (ns) | 20 |

| Speed Grade | 66 |

| Individual Output Enable Control | No |

| Minimum Operating Supply Voltage (V) | 4.5 |

| Maximum Operating Supply Voltage (V) | 5.5 |

| Typical Operating Supply Voltage (V) | 5 |

| I/O Voltage (V) | 3.3|5 |

| Maximum Operating Current (mA) | 200 |

| Minimum Operating Temperature (°C) | -55 |

| Maximum Operating Temperature (°C) | 125 |

| Supplier Temperature Grade | Military |

| Mounting | Surface Mount |

| Package Height | 4.82(Max) - 0.76(Min) |

| Package Width | 16.66 |

| Package Length | 16.66 |

| PCB changed | 44 |

| Standard Package Name | LCC |

| Supplier Package | CLCC |

| Pin Count | 44 |

| Lead Shape | No Lead |